++ 50 ++ 4bit 加算器 722755-4bit加算器 verilog

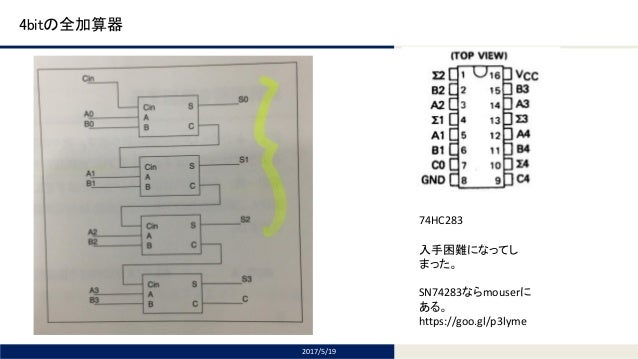

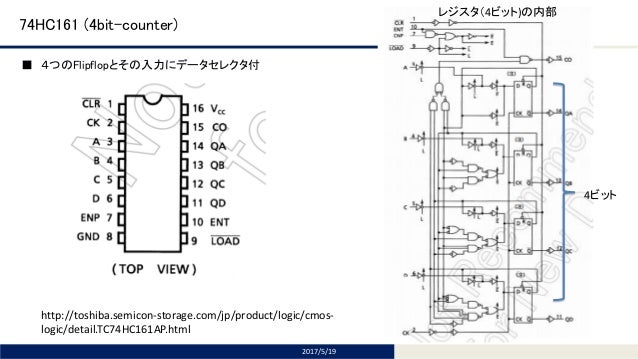

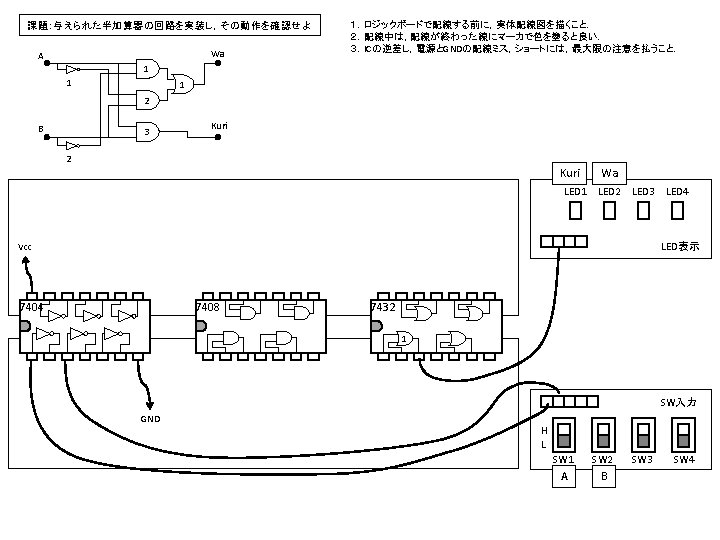

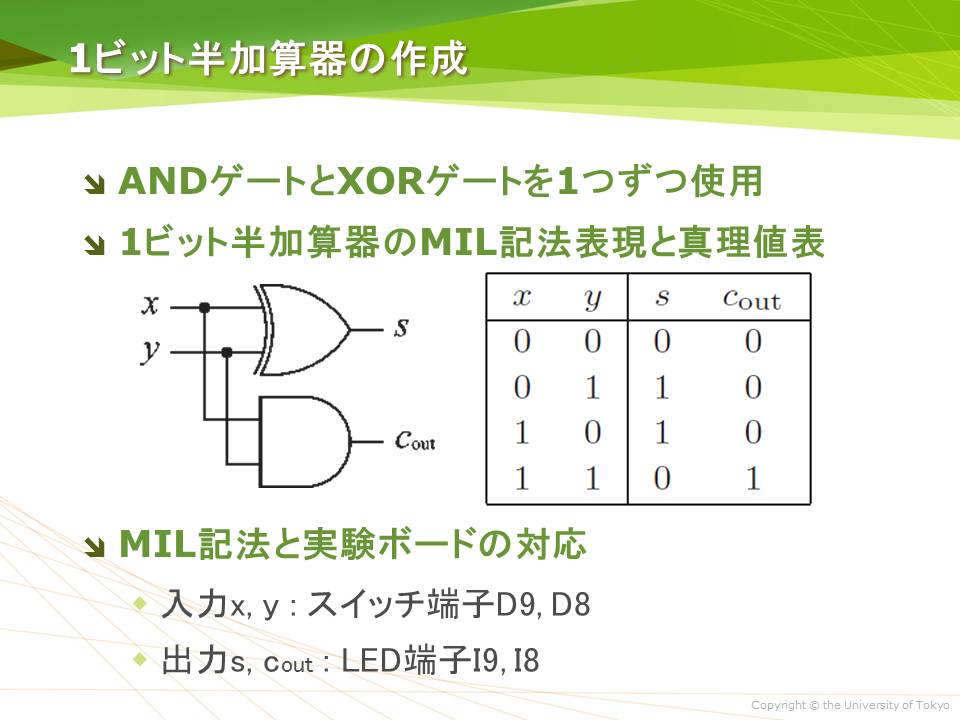

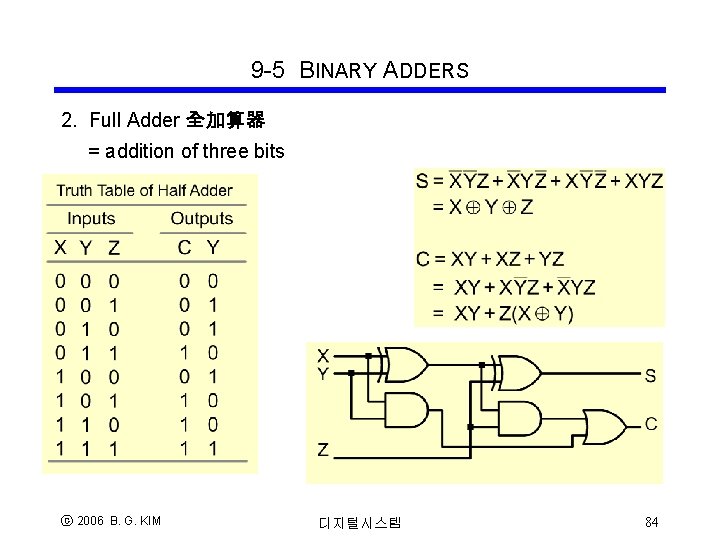

半加算器と全加算器の真理値表を図3、図4に示します。 図3半加算器の真理値表 図4全加算器の真理値表 この真理値表に従って論理回路を作ります。サム(sまたはsh)はxor、キャリー(cまたはch)はandを作ればよいのですが、マイコンの内部論理にはcmosの構成上andやorの回路は作れませ 以下全て4bitで考えます。最初に見た 0011 ) 1101 を考えます。これを符号付き整数同士の加算と考えると という正しい計算ですが、符号なし整数同士の加算と考えると という間違った計算になります。コンピュータから見ればどちらも正当な2進数の操作ですが、人間から見ると全く違う結果になります。4bitの加算器(Full Adder)74HC2を2個使っています。 74HC2は第131回と第132回で説明をしていますので、忘れてしまわれた方は、そちらのページをもう一度ご参照ください。 第179回で説明した、ALUのレジスタ"A"とレジスタ"B"からの出力を加算して、その結果をただちに出力します。 加算

ハードウェア記述言語 その2

4bit加算器 verilog

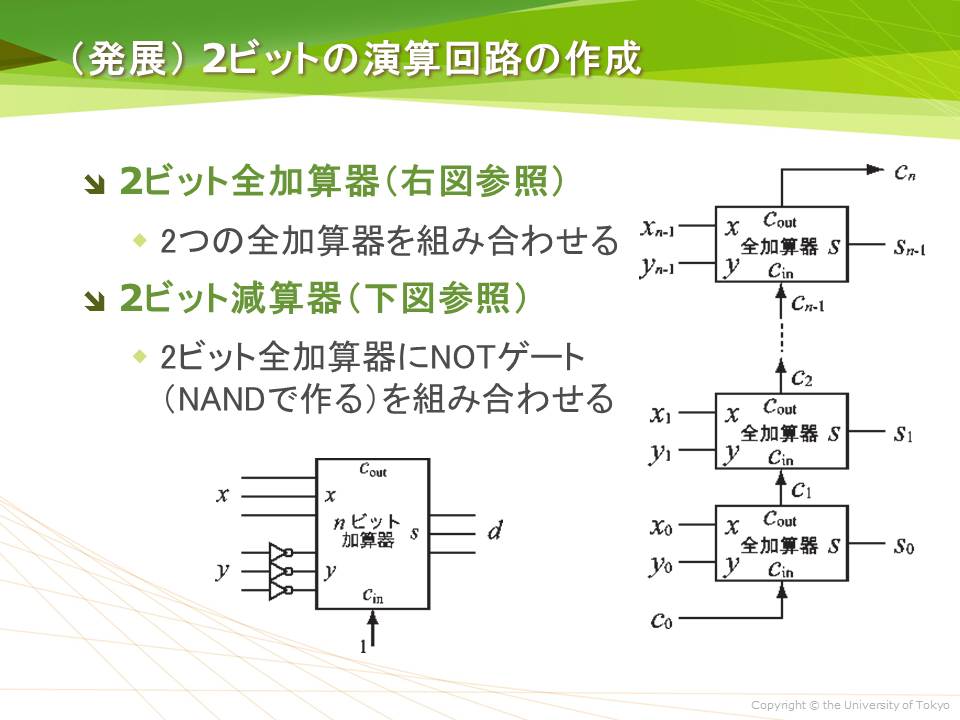

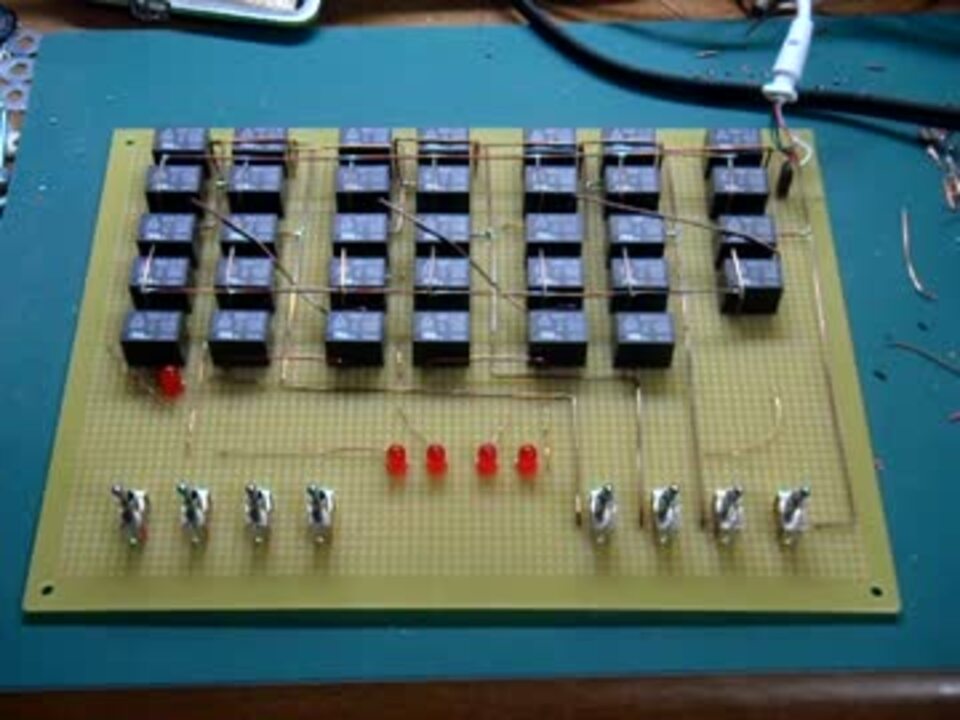

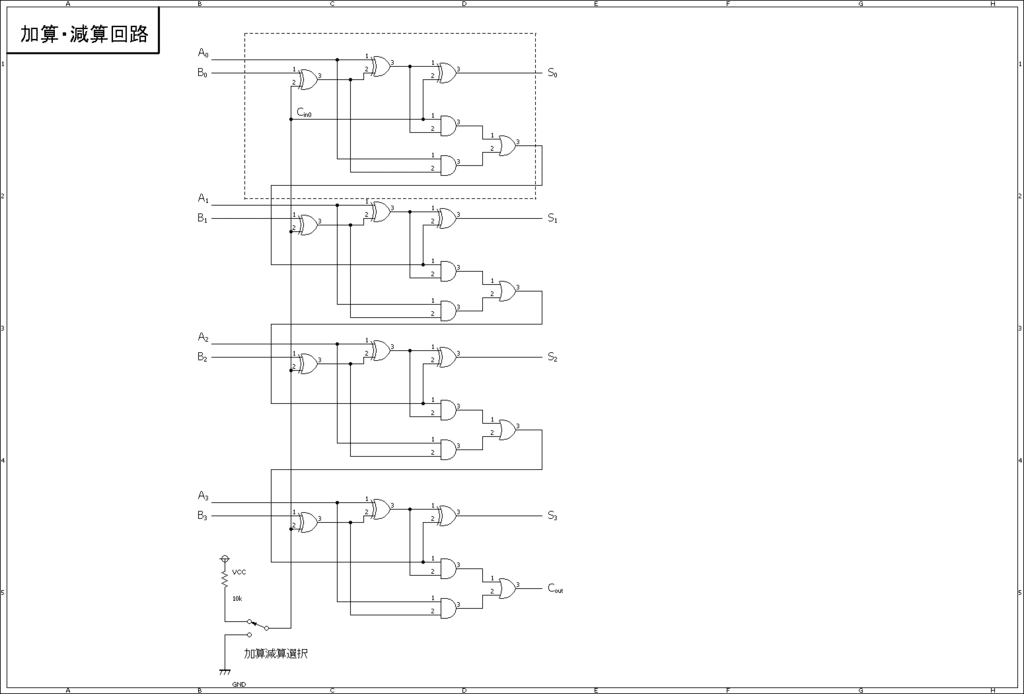

4bit加算器 verilog- リレーによる 4bit 加算回路 (4bit adder) 半加算器 や スイッチ(リレー)による半加算器 のページで、基本論理回路やリレーを使って半加算器を作れることが分かりました。 半加算器は 2 進数の 1 桁の足し算ができます。加算器 x1 x0 ci s3 s2 co fa4 x3 x2 y1 y0 y3 y2 s1 s0 fa x y co ci s fa x y co ci s fa x y co ci s fa x y co ci s x y co s fa ci 減算 除数を2 の補数に変換してから加算 x の2 の補数 2nx 例 5 (0101) の2 の補数(4ビット) 165 = 11(1011) ①全てのビットを反転させる ②1 を加える 0101 1010 1011 ① ② 減算器 x1 x0 s3 s2 co x3 x2 y1 y0 y3 y2 s1 s0 fa4 fa x y co ci s fa x y co ci s fa x

全加算器 N Bit加算器 Ushitora Lab

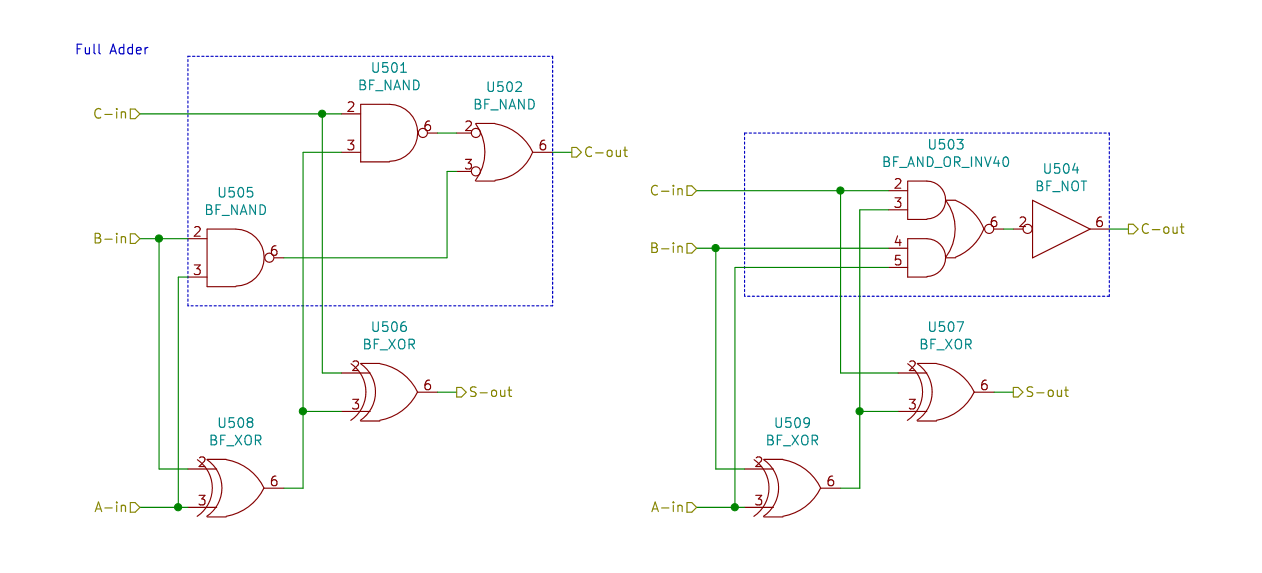

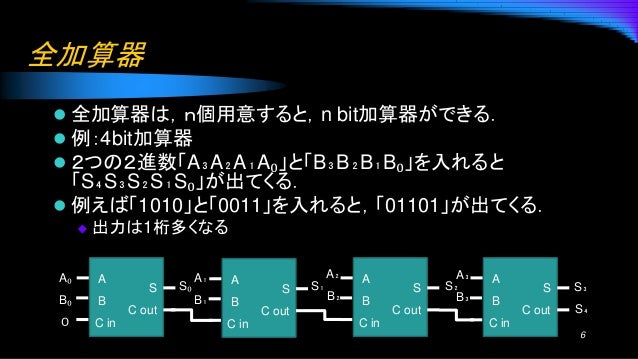

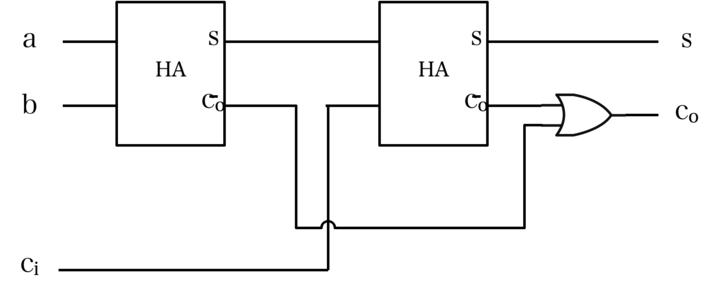

第2回 加算器(その1) 半加算器と全加算器(p52~) コンピュータは演算を行うもの、で、すべての演算は加算から導かれますから、 加算を行う加算器 (adder)は、まさにコンピュータの基本要素といえます。そして2進数で数値・データをあらわす現在のコンピュータでは、 2進数の加算を行う加算器加算器の二次元配列、対数を使わない デジタル乗算回路の設計を行う 回路規模・消費電力・演算時間の縮小 10 OUTLINE 研究背景 検討乗算アルゴリズム 検討アルゴリズム乗算回路の設計と シミュレーション検証 今後の検討回路 まとめ 15/9/14 11 検討する乗算アルゴリズム 2乗則に基づく乗算全加算器が半加算器とorゲートで出来ることが分かったので、論理回路も同じ ことです。やはり半加算器2個と1個のorゲートで出来ます。図 8と9の通りです。それぞれ の論理回路がどの式と対応しているかは分かりますよね。考えてください。全 加算器は

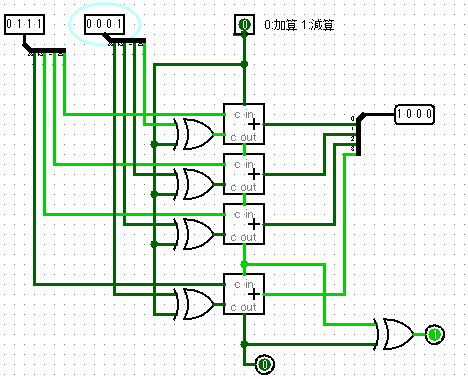

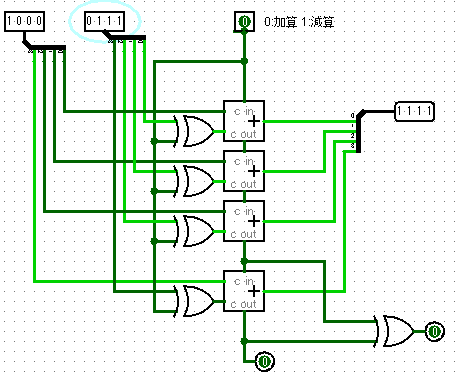

4bit 加算器 4bit adder まとめ Logisimで4bit加算器を作ってみました。次は加減算器に挑戦してみます。 関連記事 論理回路シミュレータlogisimで補数;X = 0 のとき(加算) b i ⊕0 = b i なので(b3,b2,b1,b0) はそのまま全加算器のb 入力に入る 桁上げの初期値c0 はx = 0 ⇒ 下記の回路(加算回路) と等価になる FA co s a b ci FA co s a b ci FA co s a b ci FA co s a b ci a3 b3 a2 b2 a1 b1 a0 b0 c4 s3 s2 s1 s0 c3 c2 c1 c0=0 x = 1 のとき(減算) b i ⊕1 = b4bit全加算器 OxygenNotIncluded Advanced Notes 4bit全加算器 #OxygenNotIncluded学会 #ONI計算機科学 1515までは計算できます デジタル回路における 加算器 とは、2つのデジタル信号を足した結果を計算する回路の事を言う AutomationPack以前からも加算器自体は作れた

pp 今度はライブラリーを使って4ビット加算器を作ってみる。ただの足し算で表現できる。 5LEを消費した。 library IEEE;Created Date PM減算器は加算器を用いてどうつくるか? • abなる引き算はaとbの2の補数の加算であった。 (思い出すべ し!!!!) • したがって、2の補数器と加算器で減算器が作れる。 • 2の補数=1の補数+1であった。 (思い出すべし!!!!) • 1の補数は各桁を反転したもの

リレーによる半加算器

4bit 全加算器 Cmos Dip16 Cd74hc2e Texas Instruments製 電子部品 半導体通販のマルツ

vhdlで4ビット加算器を作る / 全ビットを全加算器にしてみる 動かしてわかるCPUの作り方10講 前回はテキストどおりにビット0だけを半加算器にしたが、今度は全ビットを全加算器にしてみ全加算器を組み合わせて,複数ビットの加算をする論理回路を作る ★241 半加算器 半加算器(☆11) は,入力として2 つの1 ビットの数を受け取り,それらの和と上 ☆11) 英語でHalf Adder と いうので,HA と略記すること がある. 加算器をたくさん使う方法はハードウェアを大量に消費する上に遅いという問題がありました。Wallaceツリーは加算器に入れる前に処理を 読者になる kivantium活動日記 プログラムを使っていろいろやります 乗算器 その2 この記事はkivantium Advent Calendarの8日目です。 昨日は符号なし

4bit Cpu Td4の解説

Vhdlで4ビット加算器を作る 全ビットを全加算器にしてみる

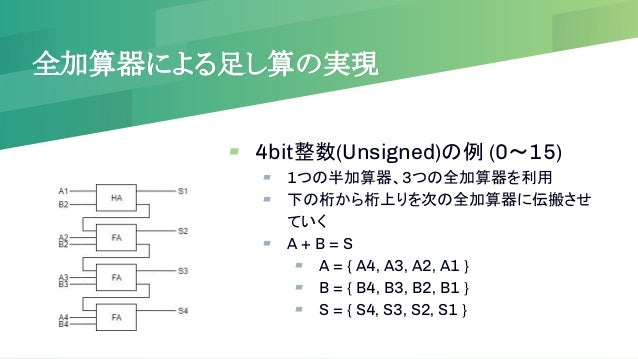

4bit加算器の例(0101 1110 = ) 上の回路を4つ接続することによって、4bitの加算器を作ることができる(下図)。Usigned数を演算するためのlibraryを使う。 entity adder_4bit_lib is port( AIN in std_logic_vector(3 downto 0);全加算器の論理式を変形する時に、どのような点を考慮して式を変形したか。 全加算器を半加算器 2 個と適当な論理演算の素子で構成する時の回路図を示しなさい。 全加算器への入力が a=0, b=1, c=1 のとき、s' と s'c の値を求めなさい。

加算器 減算器の原理 制御工学の基礎あれこれ

ハードウェア記述言語 その3

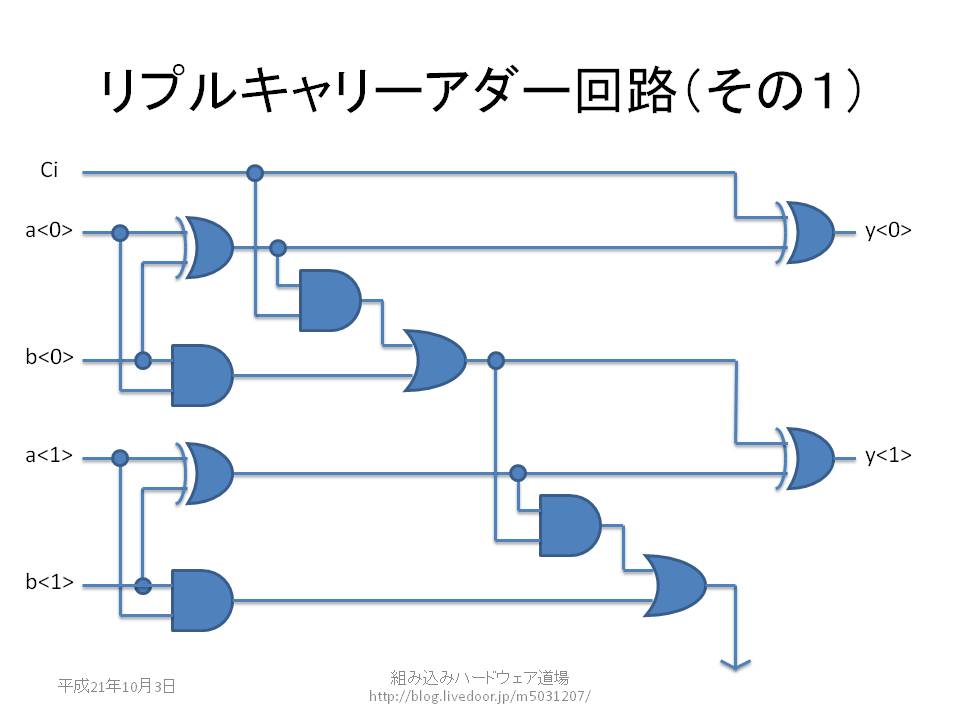

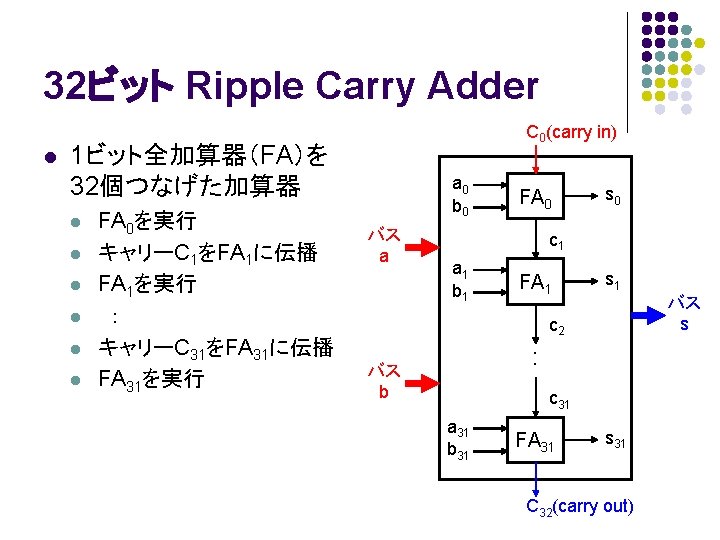

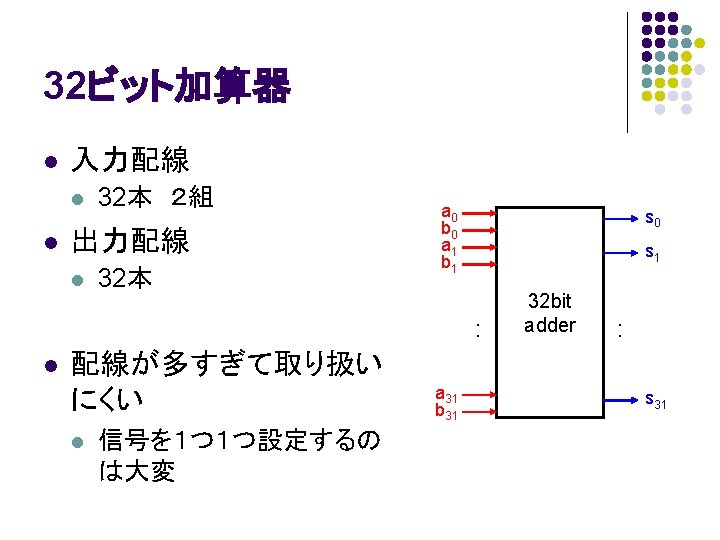

4bit 全加算器 CMOS DIP16 CD74HC2E TEXAS INSTRUMENTS製|電子部品・半導体通販のマルツ 4bit 全加算器 CMOS DIP16CD74HC2E 仕様・パッケージ:DIP16・機能:4Bit Binary Full Adder・動作電圧:2V〜6V汎用ロジッ全加算器の二次元配列を用いた乗算器 回路規模・消費電力・演算時間が大 4bitでは128bit 8bitでは4096bit Divide&Conquer法を用いることで必要なbit数を削減 34 検討するDivide & Conquer法 出力8bitの場合 上下4bitずつ分割 演算で用意する メモリを小さくできる bit数を減らして計算 シフト演算1ビット加算器を使った32ビット加算器 s31 a31 cout s1 s0 b31 b1 b0 a1 a0 cout cout cin 0 cin 下位から上位へ桁上げが伝播 ・・・ cout cin 順次桁上げ加算器 (ripple carry adder) 九州大学工学部電気情報工学科(06年度) 加算/AND/OR対応1ビットALUの設計 z仕様 z入力:a, b, cin(各1ビット) z入力:op(2ビット

4bit Cpu Td4の解説

リレーによる 4bit 加算回路

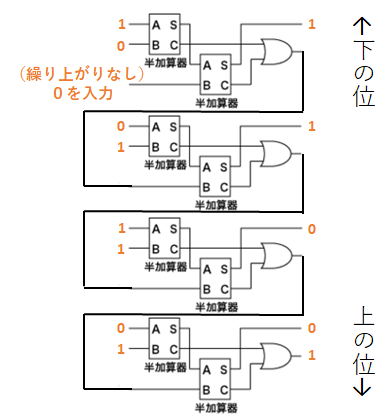

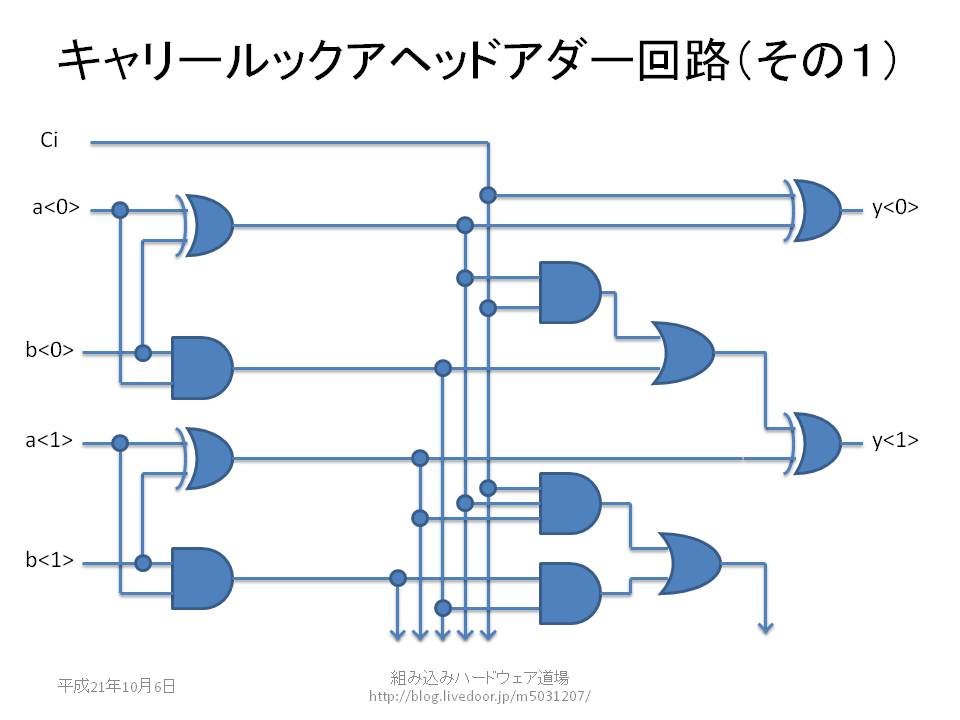

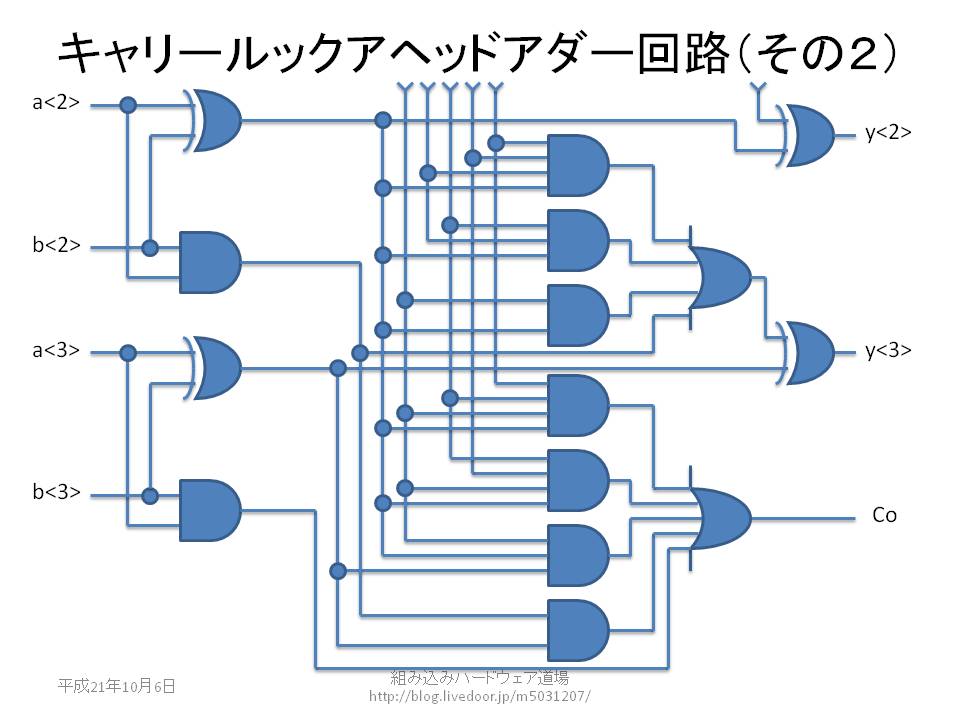

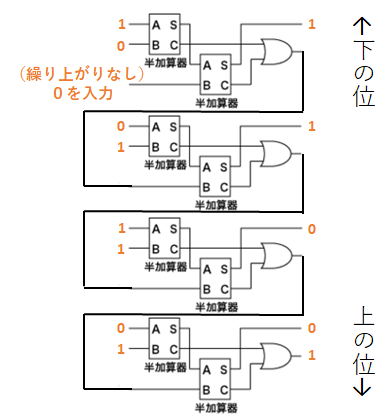

加算器 その2 この記事はkivantium Advent Calendarの4日目です。 昨日 は半加算器・全加算器・ リップル キャリーアダーを紹介しました。 リップル キャリーアダーはゲートがたくさん直列に並んでいるため遅いです。 そこで今回は高速な加算器を実装する話1 C0= A·B B·C1 C1·A S = A·B·C A·B·C A·B·C A·B·C = A·(B·C B·C) A·(B·C B·C) = A·(B⊕C) A·(B⊕C) = A⊕(B⊕C) = A⊕B⊕C 加算回路ただし、最下位桁には下位桁からのキャリーがないので、 4 ビットを加算するには 2 × 3 + 1、 実際は 7 個の半加算器があればいいことになります。 下図がその回路図です。 複雑そうに見えますが、 半加算器を単に 7 個 組み合わせただけです 。 縦に長い回路図をここでは 4 列に分けて書いてあるので、 各列の ① や ② は全部つながっています。 一番下

リプルキャリーアダー回路 組み込みハードウェア道場

File Full Adder Logic Diagram Svg Wikimedia Commons

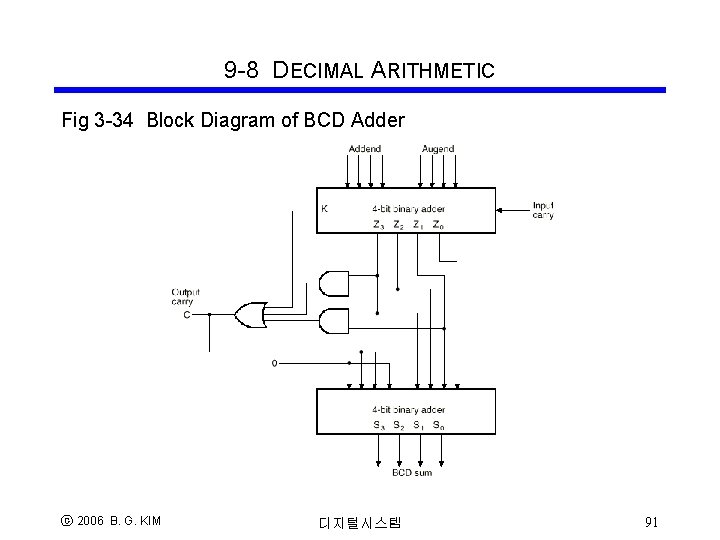

1 桁目に半加算回路(ha)、2 桁目以上に全加算回路(fa)を使用することで構成する ことができる。 たとえば、a3a2a1a0 b3b2b1b0 = cs3s2s1s0 を計算する4 ビットの加算回路は、 下図のようになる。 4 ビット加算回路 ha a b s c a fa b s c co a fa b s c co a fa b s c co ao bo a1 b1 a2 b2 a3 b3 so s1 s2 s3 c桁上げ先見加算器(CLA) CLA Carry Lookahead Adder C A B S キャリーの性質を考える 1)None のときは inに依らず out A B C C 0 0 ( , ) ( , ) 0 = = 2)Pass = 10 もしくは 01 ( , ) ( , ) ( , ) の場合 = A B out C C in 3)Generate の場合 inに依らず out A B C C 11 ( , ) ( , ) , 1 = = 桁上がり入力があると桁上がり出力が発生する 必ず 電子回路ドリル II(9) MONOist 問題9 ゲート回路の簡単化 : 完全マスター! 電子回路ドリル II(9) » 08年03月13日 00時00分 公開 横田

トラ技 年 5 月号に感化されて 4 Bit コンピュータを Mos Fet で製作する Qiita

Alu はじめてプログラム

リレー式 4Bit加算器 技術・工作 高校の文化祭で展示したら誰も説明を見ず「何コレー」カチカチ で終わったのでココに展示XORとANDの半加全加算器の真理値表は以下のようになります. (応用) 7セグメントledへの出力 1ビット全加算器から7セグメントledに出力させてみましょう. 下図のように,まず,実験ボード右奥にある7セグメントledの5v端子と電源5v端子を接続し,7セグメントledに電源を供給します. 次に,led端子i0への接続を外し,7セグメントledのa端子につなぎかえます.同様に,i1への接続About Press Copyright Contact us Creators Advertise Developers Terms Privacy Policy & Safety How works Test new features Press Copyright Contact us Creators

アーキテクチャ 4bit積算回路の設計方法 Teratail

Logisim上で作る全nandtd4

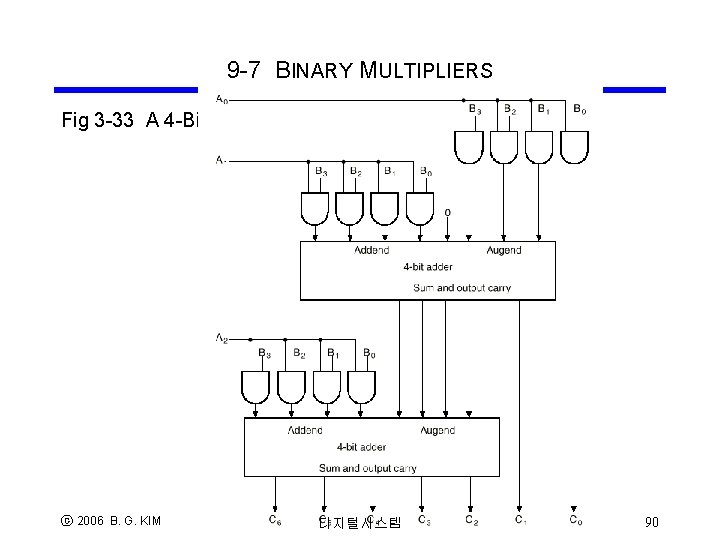

BIN in std_logic_vector(3 downto 0 この加算器はFull Adderと呼ばれ、FAと略して記載します。 4bit加算器 半加算器と全加算器を組み合わせると桁が多くなっても計算することが出来ます。具体例として59の結果を示します。 減算器 減算器は加算器で表現することが出来ます。なお、図7には含めていないが4ビット乗算器には abi を求めるための図6に示す回路が4個必要である。 図7 4ビット乗算器 図7に基づいて作成した4ビット乗算器 verilog 記述例を以下に示す。モジュール adder4 は課題1で作成した4ビット加算器である。また、モジュール multiplier4x1 は図6に示す abi を求める回路である。モジュール multiplier4x1 の記述例を図8に示す。

アーキテクチャ 4bit積算回路の設計方法 Teratail

4ビット加算器の回路図と真理値表 半加算器 全加算器付き Golden Database

論理回路シミュレータlogisimで加算回路 はじめてプログラム

Logisim上で作る全nandtd4

4 演算回路の作成

1999 号 乗算器 Astamuse

Http Www Ed Noda Tus Ac Jp Jte401 Files 19 Text 2 Pdf

リレーでつくる4ビット2進加算器

通販 Tc74hc2ap 74hc2 4bit並列全加算器 Hcシリーズ 16pindip ビスパの電子販売

Logisim上で作る全nandtd4

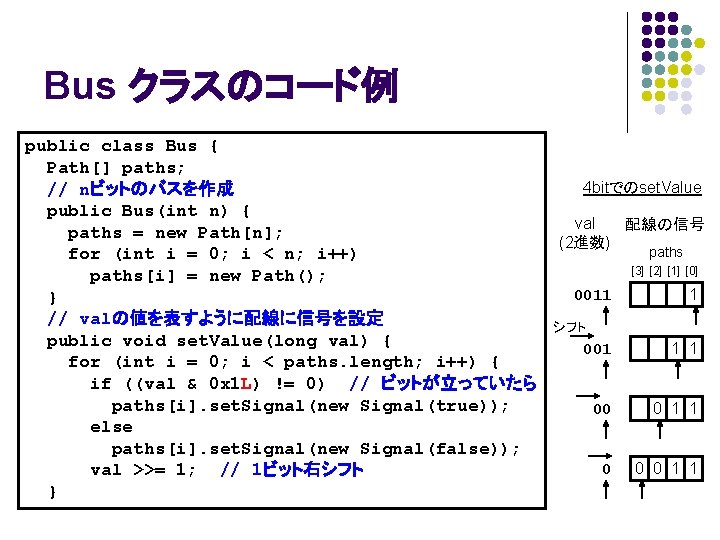

Bus Public Class Bus Path Paths N Public

ロボット技術研究会回路講習会17 4

シンクロナイザ 非同期入力の同期化

加算器 減算器の原理 制御工学の基礎あれこれ

Alu はじめてプログラム

情報画像工学実験ii 実験6 論理回路設計

Mixed Signal Systems And Integrated Circuits Pdf Free Download

組合せ回路の例 加算回路

リレー式 4bit加算器 ニコニコ動画

キャリールックアヘッドアダー回路 組み込みハードウェア道場

にがてぶろぐ

情報画像学実験ii 実験1 論理回路

4bit全加算器 Oxygennotincluded Advanced Notes

レジスタ セレクタ にalu 4bit全加算器 をつなげた Weed Flickr

ハードウェア記述言語 その2

Fpga入門 備忘録 組み合わせ回路編 ハードウェアエンジニアの備忘録

番外編 chap 5 ラダー図で加算器をつくる 2

ハードウェア記述言語 その2

Vhdlの4ビット加算器 Ja Pays Tarusate Org

組合せ回路の例 加算回路

Test04 回路を部品化する にがてぶろぐ

1 Digital System What Why How 2 Binary

リレー式全加算器を作る 数に溺れて

Bus Public Class Bus Path Paths N Public

Logisim上で作る全nandtd4

Vhdlの4ビット加算器 Ja Pays Tarusate Org

Bus Public Class Bus Path Paths N Public

回路図 ヘキサドライブ日記

4bit加算器 2 写真共有サイト フォト蔵

Ltspice 全加算器を作成する Miraiportal

1 Digital System What Why How 2 Binary

積算回路 ヘキサドライブ日記

加算器 減算器の原理 制御工学の基礎あれこれ

キャリールックアヘッドアダー回路 組み込みハードウェア道場

4ビット加算器の回路図と真理値表 半加算器 全加算器付き Golden Database

組合せ回路の例 加算回路

4 組合せ回路 Digital Electronic Circuits 1 0 ドキュメント

4 組合せ回路 Digital Electronic Circuits 1 0 ドキュメント

Logic Simulator Full Adder Tinkercad

Mlctbbase Sw Box On 4511 7 Led Gnd

全加算器 N Bit加算器 Ushitora Lab

論理ゲートをpythonで作ってcpuを学ぶ 第1回 Qiita

1997 号 論理演算回路及びキャリールックアヘッド加算器 Astamuse

Vhdlで4ビット加算器を作る ライブラリーを使う

第2回

加算器 減算器の原理 制御工学の基礎あれこれ

2進10進変換回路

1999 号 桁上げ先見回路および並列加算器 Astamuse

Halfadder Instagram Posts Gramho Com

リレー式 4bit加算器 Youtube

全加算回路 四国の電子工作オタク

足し算をつくろう

Cpuよもやま話 論理ゲートを使って加算器を作ってみよう Vbaの勉強を始めてみた

Chap9

8 Bit Adder Systemmodeler Model

加算回路をmil記号を用い図示せよとの問題について Okwave

ttlでcpuを作ろう

1995 1913号 演算器 Astamuse

ディジタル電子回路 論理回路のマルチシム

第2回

Cpuよもやま話 論理ゲートを使って加算器を作ってみよう Vbaの勉強を始めてみた

割り算回路 その2

4 演算回路の作成

トラ技 年 5 月号に感化されて 4 Bit コンピュータを Mos Fet で製作する Qiita

16 Bit Cellular Cla Adder Download Scientific Diagram

1999 号 乗算器 Astamuse

Experiment 実験 組み合わせ回路と順序回路を体験するため 以下の2つの回路を組みました 当日は実際に回路を展示します 加算回路加算回路は組み合わせ回路の簡単な例です 今回は 全加算器を4つ用いて4bit 4bitの加算回路を組みました 実際に

Ie U Ryukyu Ac Jp Wada Digcir11 Digcirhandout7 Pdf

リレーで4ビット2進加算器を作る 数に溺れて

4bit全加算器 Oxygennotincluded Advanced Notes

Mixed Signal Systems And Integrated Circuits Pdf Free Download

Schematic Entry 4 Bit Carry Look Ahead Adder

4ビット加算器の回路図と真理値表 半加算器 全加算器付き Golden Database

もりとにーのブログ Logisimでtd4を再現したお話 ポエム

1 Digital System What Why How 2 Binary

File 4 Bit Carry Lookahead Adder Svg Wikimedia Commons

コメント

コメントを投稿